Материал взят из книги

Скачать оригинал КНИГИ в хорошем качестве

_Основы

микропроцессорной

техники

Типовая схема микропроцессорной системы

если вы внимательно прочитали предыдущую главу и поняли все, о чем в ней говорится, то теперь можно приступать к новому этапу. Рассмотрим более детально, как устроена типичная микропроцессорная система. На рис. 29 приведена ее обобщенная структурная схема.

На схеме показаны все основные элементы микропроцессорного устройства. Для удобства все названия даны в русском и английском вариантах. Обнако учтите, что в реальной практике вам придется иметь дело почти исключительно с английскими обозначениями. Расшифруем все эти обозначения. Каждый термин я даю сначала в его международном английском варианте, затем расшифровку на английском языке. Далее идет дословный перевод и в конце принятые у нас название и сокращение.

CPU (Central Processing Unit) — центральный процессор или центральное процессорное устройство (ЦПУ).

RAM (Random Access Memory) — устройство с произвольным доступом, или оперативное запоминающее устройство (ОЗУ).

ROM (Read Only Memory) — память только для чтения, или постоянное запоминающее устройство (ПЗУ).

Port I/O (Port Input/Output) — порт ввода/вывода.

Что такое процессор вы уже немного знаете из первой главы нашей книги. ОЗУ и ПЗУ — это два вида памяти. Их можно было бы не разделять. Процессор, например, их и не различает и работает с обоими видами памяти абсолютно одинаково. Но между двумя этими видами

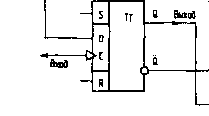

памяти есть одно довольно существенное различие. ОЗУ хранит информацию только при наличии напряжения питания. Классический пример ячейки ОЗУ — это простейший регистр, построенный на О-триг-герах (см. рис. 27). В такой регистр можно записывать информацию и читать ее оттуда. Она там будет храниться все время, пока на схему подано питание. Но после выключения питания при последующем его включении все О-триггера регистра установятся в случайное положение. Информация будет утеряна.

В настоящее время для построения схем ОЗУ применяют совсем другие технологии. Однако и по сей день не придумано достаточно быстродействующее устройство памяти, не теряющее информации при выключении питания. Современное ОЗУ строится на основе динамически подзаряжаемых миниатюрных емкостей, выполненных интегральным способом на кристалле кремния. Это, так называемое, динамическое ОЗУ. Каждый конденсатор хранит один бит информации. Входной сигнал через внутренние схемы коммутации поступает на этот конденсатор. Если его значение равно логической единице, то конденсатор заряжается. Если логическому нулю — то разряжается. Затем внутренний ключ отключает конденсатор от всех цепей и заряженные конденсаторы какое-то время хранят свой заряд.

Но эти конденсаторы имеют очень маленькую емкость. Поэтому свой заряд они держат всего лишь несколько миллисекунд. Для того, чтобы информация ни потерялась, используют схему регенерации памяти. Все ячейки памяти организуются, как набор строк. Специальная схема периодически считывает информацию из памяти строка за строкой. После считывания очередной строки, считанная информация опять записывается в те же ячейки памяти. Конденсаторы при этом подзаряжаются

снова. Для нормальной работы динамического ОЗУ схема микропроцессорного устройства должна непрерывно обеспечивать такую регенерацию в течение всего времени работы системы. ОЗУ современных больших компьютеров также устроено по динамическому принципу. Однако схема регенерации встроена внутрь самих микросхем ОЗУ.

Постоянное запоминающее устройство ПЗУ предназначено для долговременного хранения информации. Информация, хранящаяся в ПЗУ, не пропадает при выключении питания. Зато ее нельзя оперативно менять. Информация в ПЗУ записывается один раз либо в процессе их производства, либо непосредственно перед применением, при помощи специальных программаторов. Принцип хранения информации в микросхемах ПЗУ основан на пережигании специальных внутренних перемычек. Каждая перемычка предназначена для хранения одного бита информации. Если перемычка цела, то это значит, что в данной ячейке хранится единичный бит информации. Если прожечь перемычку, то соответствующий бит примет нулевое значение.

Хотя процессор и работает с обоими видами памяти одинаково, он может только читать информацию из ПЗУ. Запись информации в ПЗУ невозможна. Если микропроцессор все же попытается произвести запись, то ничего страшного не произойдет. Просто в ячейке останется то, что там было до попытки записи.

Порты ввода/вывода можно рассматривать как вместе, так и отдельно: порты ввода и порты вывода. Дело в том, что процессор работает с портами ввода/вывода практически так же, как и с ячейками памяти. У каждого порта есть свой собственный адрес. Причем адрес ячейки памяти и адрес порта ввода/вывода — это абсолютно разные адреса. Они находятся, как говорят, в разных адресных пространствах. Процессор может записать любое число в.любой порт ввода/вывода. Затем он может считать число из порта по тому же адресу. Иногда это будут одни и те же числа. Но чаще запись происходит в одно устройство (порт вывода), а читает процессор уже из другого (порта ввода).

В качестве порта вывода можно применить обыкновенный параллельный регистр. Порт вывода предназначен для того, чтобы микропроцессорная система могла управлять различными внешними устройствами. При помощи порта вывода можно управлять такими устройствами, как, например, цифро-аналоговые преобразователи (ЦАП), индикаторы. К выходам порта можно подключать электронные ключи, которые позволят микропроцессорной системе управлять более мощными устройствами. Такими, как электромагнитные реле, лампочки, светодиоды, моторчики, соленоиды и т.д. При помощи портов вывода можно даже делать переключения в самой схеме микропроцессорного устройства. Это делается при помощи ключей и логических элементов. Такое микропроцессорное устройство становится гибким и способным автоматически подстраиваться под выполняемую задачу.

Порт ввода — это специальная схема, при помощи которой микропроцессор может принимать внешние данные. К этим входам можно подключать аналого-цифровые преобразователи (АЦП), кнопки, датчики и т.д.

Главным управляющим элементом всей микропроцессорной системы является процессор. Именно он, за исключением нескольких особых случаев, управляет всеми остальными устройствами. Остальные же устройства, такие, как ОЗУ, ПЗУ и порты ввода/вывода являются ведомыми. По этой причине их еще называют «периферийными устройствами» или «периферией».

Все узлы микропроцессорной системы соединены между собой при помощи трех основных шин:

шд — шина данных (DATA bus).

ША — шина адреса (ADDR bus).

ШУ — шина управления (CONTROL bus).

Все вместе они образуют системную шину. Мы уже немного знакомы с шиной данных. Сейчас нам нужно познакомиться со всеми видами микропроцессорных шин. Начнем по порядку.

Эта шина предназначена для передачи данных от микропроцессора к периферийным устройствам, а также в обратном направлении. Разрядность шины данных определяется типом применяемого процессора. В простых микропроцессорах шина данных обычно имеет 8 разрядов. Современные процессоры могут иметь шину данных на 16, 32, 64 разряда. Количество разрядов всегда кратно восьми. Двоичное число, имеющее восемь разрядов, называется байтом.

В вычислительной технике байт, по сути, стал минимальной единицей информации. Шестнадцатиразрядная шина данных может за раз передавать до двух байтов. 32-разрядная шина передает до четырех байт. 64-разрядная — до восьми. Однако во всех этих шинах обязательно предусмотрен режим передачи одного байта (по младшим его разрядам). Старшие разряды при этом не используются.

Как и шина данных, шина адреса представляет собой набор проводников, по которым происходит передача двоичных чисел в электронной форме. Однако, в отличие от шины данных, двоичные числа, передаваемые по шине адреса, имеют другой смысл и назначение. Они представляют собой адрес ячейки памяти или порта ввода/вывода, к которому в данный момент обращается процессор. Количество разрядов адресной шины отличается большим разнообразием. Например, микропроцессор серии К580ИК80 имеет 16 разрядов адреса. Это можно считать минимальным количеством.

Процессор 1ме1 8086, на котором собран родоначальник всех РС-со-вместимых персональных компьютеров — компьютер 1ВМ РС-ХТ, имеет 20 разрядов шины адреса. Современные процессоры имеют до 32 разрядов и больше. От количества разрядов шины адреса зависит то, какое количество ячеек памяти может адресовать процессор. Процессор, имеющий шестнадцатиразрядную шину данных, может обращаться к 216 (то есть к 65536) ячейкам памяти. Это число называется объемом адресуемой памяти. Реальный объем подключенной памяти может быть меньше, но никак не больше этой величины.

В вычислительной технике используется необычный способ для измерения объема памяти. Объем памяти измеряется в байтах, килобайтах, мегабайтах и т.д. Один килобайт в вычислительной технике не равен 1000 байтов, как этого можно было бы ожидать. Это связано с тем, что объем памяти, подчиняется уже знакомому нам закону. Он всегда будет равен какой-либо степени двойки. То есть он всегда равен 2", где п — любое целое число. По этой причине один килобайт равен 1024 байтов. Такое значение с одной стороны максимально приближается к числу 1000. А с другой стороны 1024 равно 210.

Для того, чтобы вы смогли окончательно разобраться в этом вопросе, приведу один небольшой пример. Для адресации 1024 ячеек памяти нужна шина адреса, имеющая ровно 10 разрядов. При этом, если мы подключим к ней именно столько ячеек памяти, шина не будет избыточна. Если бы мы захотели иметь только 1000 ячеек, то для обращения к любой из этих ячеек, нам все равно потребовалось бы 10 разрядов адреса, так как если разрядов будет девять, то мы сможем обратиться только к 512 ячейкам. Именно поэтому никто и никогда не делал запоминающего устройства с объемом не 2П. Логично, что и объем памяти удобнее измерять в величинах, взятых из того же ряда.

Данный принцип распространяется и на более высокие размерности. Один мегабайт равен 1024 килобайтам. Один гигабайт равен 1024 мегабайтам. Ну. и так далее.

Для адресации портов ввода/вывода также нужна шина адреса. В обоих случаях в этой роли выступает одна и та же шина. Но ни одной микропроцессорной системе никогда не может потребоваться такое же большое количество портов ввода/вывода, сколько обычно бывает ячеек ОЗУ. Поэтому, в процессе обмена с портами ввода/вывода процессор использует только восемь (реже 16) младших разрядов шины адреса.

Эта шина не имеет такой же четкой структуры, как шина данных или шина адреса. В шину управления условно объединяют набор линий, передающих различные управляющие сигналы от процессора на все периферийные устройства и обратно. Что же это за линии. В любой шине управления обязательно присутствуют линии, передающие следующие сигналы:

RD (Read) — сигнал чтения.

WR (Write) — сигнал записи.

MREQ — сигнал инициализации устройств памяти (ОЗУ или ПЗУ). IORQ — сигнал инициализации портов ввода/вывода.

Кроме того, к сигналам шины управления относятся:

READY — сигнал готовности.

RESET — сигнал сброса.

И еще несколько специальных сигналов, о которых мы поговорим позже.

Все, что было сказано выше, описывает общие принципы построения микропроцессорных устройств. В данной книге мы будем рассматривать гораздо более узкий вопрос. Мы будем изучать простую микропроцессорную систему, имеющую восьмиразрядную шину данных и шестнадцатиразрядную шину адреса.

Рассмотрим подробнее, как работает микропроцессорная система, изображенная на рис. 29. Как уже говорилось, в основном режиме работы всей микропроцессорной системой управляет центральный процессор (CPU). При этом, по отношению к любым периферийным устройствам, процессор может выполнять в каждый момент времени одну из четырех основных операций: чтение из ячейки памяти, запись в ячейку памяти, чтение из порта и запись в порт.

Для того, чтобы прочитать байт из ячейки памяти, процессор сначала устанавливает на шине данных адрес нужной ячейки. Затем он устанавливает сигнал MREQ в активное состояние, то есть устанавливает его равным логическому нулю. Этот сигнал поступает на устройства памяти и служит разрешением для их работы. При этом сигнал IORQ остается равным лог. 1. Поэтому порты ввода/вывода микропроцессорной системы остаются не активными. Далее, процессор переводит в активное состояние сигнал RD. Этот сигнал поступает как на устройства памяти, так и на порты ввода/вывода. Однако порты не реагируют на него, так как они отключены высоким уровнем сигнала IORQ. Устройство памяти напротив, получив управляющие сигналы RD и MREQ, выдает на шину данных байт информации из той ячейки памяти, адрес которой присутствует в этот момент на шине адреса.

Процесс записи данных в память происходит в следующей последовательности. Сначала центральный процессор выставляет на адресную шину адрес нужной ячейки памяти. Затем на шину данных он выставляет байт, предназначенный для записи в эту ячейку. После чего активизируется сигнал MREQ, разрешающий доступ к модулю памяти. И уже затем процессор устанавливает сигнал WR в активное состояние (лог. 0). Именно по этому сигналу происходит запись байта в ячейку памяти, адрес которой присутствует на шине адреса.

Некоторые виды памяти работают очень медленно. Они могут не успеть выдать информацию или произвести ее запись так быстро, как это способен сделать центральный процессор. Для согласования работы медленных устройств памяти с быстрыми процессорами существует сигнал READY (готовность). Сразу после того, как процессор установит сигнал чтения или записи в активное состояние, устройство памяти устанавливает сигнал READY в пассивное состояние (лог. 0). Такой уровень сигнала означает, что внешнее устройство не готово, то есть еще не выполнило команду. Сигнал READY поступает на процессор, и процессор переходит в режим ожидания. Когда устройство памяти выполнит текущую команду, оно устанавливает сигнал READY в активное состояние (лог. 1). Процессор, получив этот сигнал, возобновляет работу. Сигнал READY применяется и в случае работы с медленными портами ввода/вывода.

Г

Операции чтения из порта и записи в порт происходят аналогично операциям чтения/записи ОЗУ. Различие лишь в том, что вместо сигнала MREQ в активное состояние переходит сигнал IORQ, разрешающий работу портов.