Материал взят из книги

Скачать оригинал КНИГИ в хорошем качестве

В предыдущем разделе мы узнали, что для хранения информации можно использовать даже простейший ЯБ-триггер. Но в цифровой техники имеются элементы более подходящие для этой цели. К ним можно отнести О-триггеры, Ж-триггеры и, основанные на них, различные регистры. Рассмотрим все это по порядку.

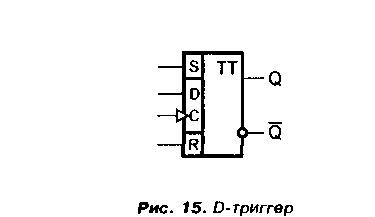

Начнем с О-триггера. Схемное обозначение типичного О-триггера приведено на рис. 15. На рисунке изображен не просто О-триггер, а комбинированный элемент, в котором элементе объединены два триггера. Как видно из рисунка, у этого составного элемента имеются уже знакомые нам входы Я и Б. Если использовать только эти входы, то мы получим обычный ЯБ-триггер. При работе в режиме О-триггера на входах Я и Б должен присутствовать сигнал лог. 1. В этом режиме переключение триггера происходит под воздействием сигналов на входах О и С.

Вход С называется тактовым. На него поступает тактовый импульс, по которому и происходит запись. Обратите внимание, что на условном обозначении триггера тактовый вход отмечен стрелкой в виде маленького треугольника. Такой треугольник означает, что данный вход импульсный. До сих пор мы имели дело с потенциальными входами. Потенциальный вход реагирует на потенциал поступающего, на него сигнала. А импульсный вход на изменение этого сигнала. Различают импульсные входы, работающие по фронту и по спаду импульса. Фронтом импульса называют момент перехода от низкого логического уровня к высокому. А спадом — переход от высокого уровня к низкому. Иногда используют другие термины: передний фронт и задний фронт импульса.

Вход D — это вход данных (DATA). На него подается логический уровень, который необходимо записать в D-триггере.

Если на вход О-триггера подать сигнал логической единицы, а на вход С импульс записи, то по спаду этого импульса триггер установится в единичное состояние. Если в момент спада импульса записи на входе О окажется логический ноль, то триггер установится в нулевое состояние. Такая логика работы О-триггера делает его очень удобным устройством для хранения одного бита цифровой информации.

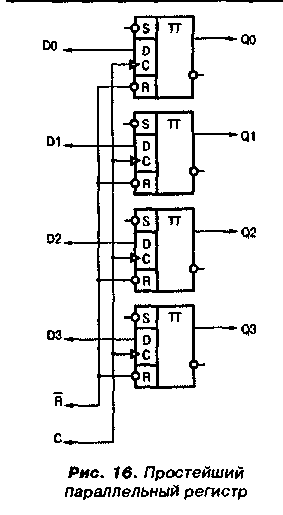

Для хранения двоичного числа, состоящего более чем из одного разряда, используют несколько параллельно соединенных О-триггеров. На рис. 16 показана схема, предназначенная для хранения четырехразрядного двоичного числа. Такая схема называется параллельным регистром. Для того, что бы сохранить какое-либо число в таком регистре, нужно подать это число на входы О0...ОЗ. Затем на вход С схемы подается импульс записи. По заднему фронту этого импульса число записывается в регистр. Причем каждый разряд числа записывается в свой отдельный О-триггер. Записанное в регистр число можно считывает из него при помощи выходов 00...03.

Вход Я используется для начальной установки всех разрядов регистра в нулевое состояние. Это бывает важно в том случае, когда регистр используется для управления внешними устройствами. Сигнал сброса на вход Я подают обычно в момент включения питания.

Обратите внимание на обозначение входа Я. Мы впервые имеем дело с инверсным входом! Такое обозначение применяется не всегда. Применяя его, мы подчеркиваем, что активным значением для входа является логический ноль. Именно при подаче логического нуля происходит сброс триггера.

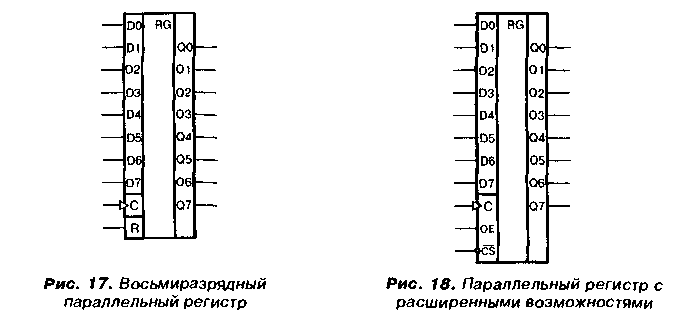

В реальных микропроцессорных устройствах чаще используются восьмиразрядные параллельные регистры. На

рис. I / изооражен такой регистр, его внутренняя структура и назначение выводов аналогичны структуре регистра, изображенного на рис. 16.

Более сложный регистр изображен на рис. 18. Это регистр гораздо более приспособлен для работы с параллельной шиной данных. Для это-го в регистр введены два новых входа: вход выбора микросхемы (СБ) и вход перевода выходов в высокоимпедансное состояние (ОЕ).

Разберемся подробнее с этими новыми входами и режимами.

Вход выбора микросхемы CS (Chip Select) предназначен для ее включения и выключения в разные моменты времени. Такие входы можно часто встретить у микросхем, предназначенных для микропроцессорной техники. Особенно в больших, многофункциональных микросхемах. Наличие таких входов позволяет соединять несколько подобных микросхем параллельно, но работать с каждой по отдельности. В случае параллельного соединения нескольких регистров, таких, как изображены на рис. 18, можно соединить вместе одноименные входы данных (DO с DO, D1 с D1, и т.д.), а также входы синхронизации С. Поданные на входы D0...D1 данные будут записаны только в тот из регистров, на вход CS которого в момент записи будет подан низкий логический уровень. Состояние остальных регистров останется неизменным.

Вход ОЕ, напротив, используется при параллельном объединении нескольких регистров по их выходам. Такое объединение возможно только в том случае, если в каждый момент времени будут работать выходы только одной из микросхем. Выходы остальных параллельно соединенных микросхем должны уметь автоматически отключаться от схемы. Для этой цели описываемый регистр имеет специальный режим. В этом режиме все выходы микросхемы отключаются и не влияют на работу остальной схемы. При этом сопротивление паразитной нагрузки, которую создает микросхема, подключенная к шине данных настолько велико, что не создает помех в работе шины. Такое состояние выходов называется высокоимпедансным. Импеданс — это полное сопротивление цепи (активное — по постоянному току, плюс реактивное — по переменному).

Описываемая микросхема переводит свои выходы в высокоимпеданс-ное состояние при подаче логической единицы на вход ОЕ. Если же на вход ОЕ подать логический ноль, то выходы микросхемы перейдут в рабочее состояние.

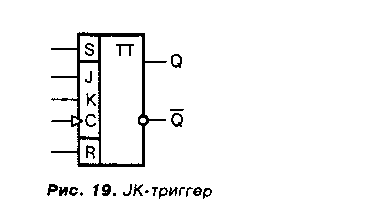

Напоследок хочу рассказать об еще одном виде триггеров — о Ж-триг-гере. Условное обозначение такого триггера приведено на рис. 19. Как

видно из рисунка, вместо одного Э-входа такой триггер имеет два входа — .1 и К. Логика работы такого триггера более сложна. Если на 3-вход подать сигнал логической единицы, а на К-вход — сигнал логического нуля, то по спаду тактового сигнала триггер установится в единичное состояние. Если на .1 подать лог. О, а на К — лог. 1, то по спаду тактового импульса триггер установится в нулевое состояние. Если на обоих информационных входах лог. 1, то по каждому спаду тактового импульса триггер будет переключаться в другое, противоположное состояние. И, наконец, если на оба входа Ж-триггера подать сигнал логического нуля, то триггер перестанет реагировать на тактовые импульсы, и все время будет оставаться в одном и том же состоянии.

На первый взгляд логика работы триггера чересчур сложна и область применения таких триггеров не очевидна. Однако виртуозы схемотехники умудряются при помощи Ж-триггеров создавать более компактные и рациональные схемы. Чаще всего Ж-триггер применяется для построения различных счетчиков и делителей. А вот что такое счетчики мы узнаем из следующего раздела.