Материал взят из книги

Скачать оригинал КНИГИ в хорошем качестве

Система команд микроконтроллера АТ89С2051

Система команд микроконтроллера АТ89С2051 насчитывает 107 команд, из них 45 однобайтовых, 45 двухбайтовых и 17 трехбайтовых. Все команды выполняются за один или два машинных цикла (12 тактов ALE) за исключением команд MUL и D1V, которые требуют четыре цикла. Большинство двухбайтовых команд одноцикловые, а все трехбайтовые команды — двухцикловые. Это объясняется тем, что за один машинный цикл может считываться до двух байтов, программного кода. Все множество команд удобно разбить на пять групп:

■ Команды пересылки (25).

■ Команды логической обработки (25).

■ Арифметические команды (24).

■ Команды передачи управления (17).

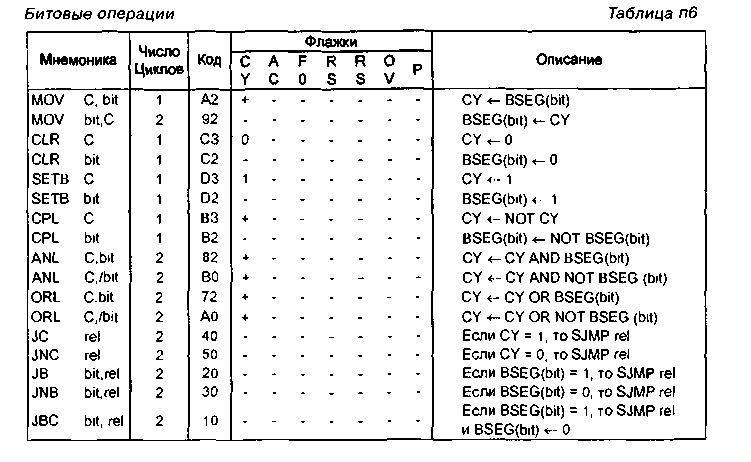

■ Битовые команды (17).

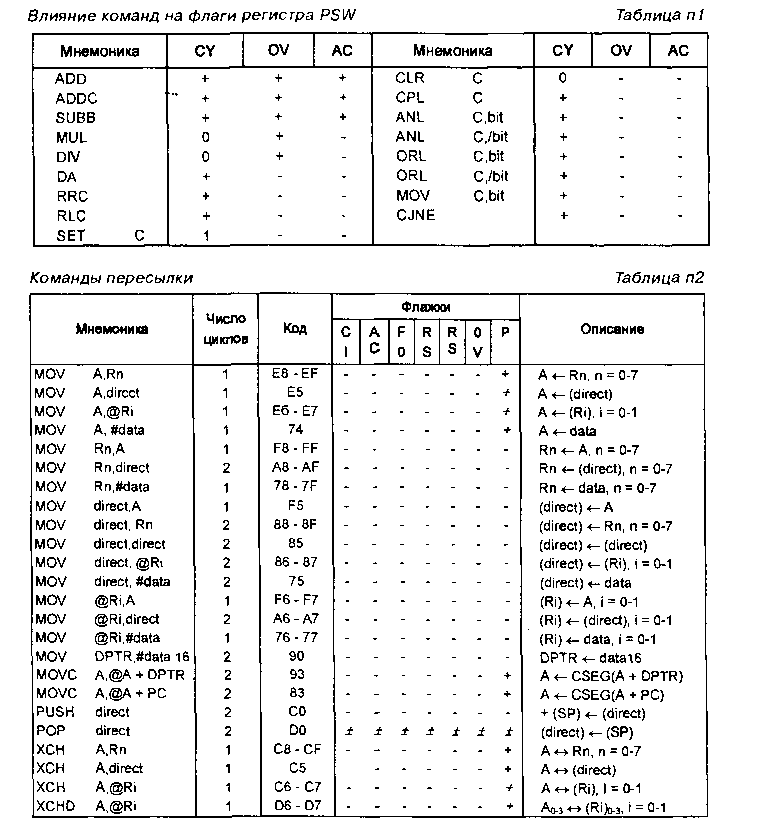

В процессе исполнения, команды влияют на ряд флажков-признаков результата, входящих в состав PSW (табл. п1). Признак Р устанавливается всякий раз, когда приемником результата служит аккумулятор, включая операции пересылки.

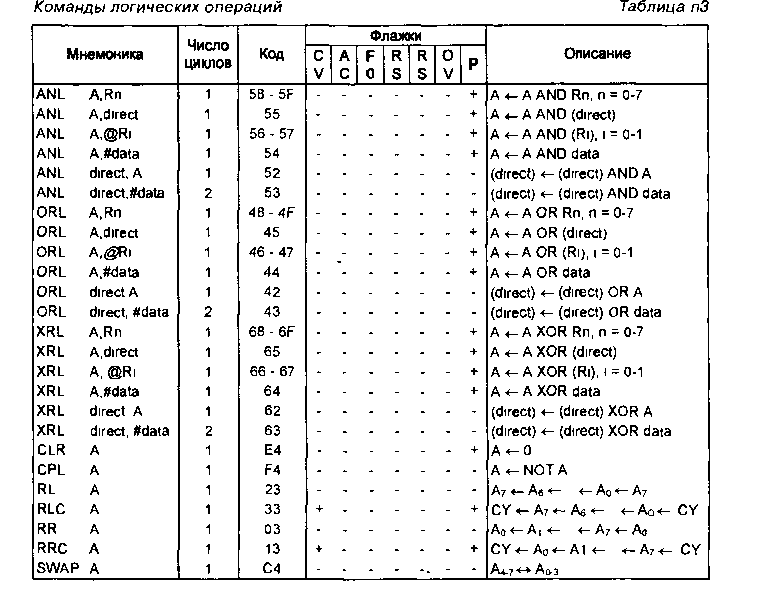

Группа команд пересылки (табл. п2) содержит команды MOV (пересылки данных между DSEG и RSEG), MOVC (между CSEG и А), команды обращения к стеку PUSH и POP, а также две команды обмена ХСН и XCHD.

Наиболее емкой инструкцией является команда MOV, которая использует четыре способа адресации: регистровый (A, Rn, DPTR), прямой (direct), косвенный (@Ri) и непосредственный (#data, #datal6). Для указания приемника служат три способа адресации (кроме непосредственного), для указания источника — все четыре. Трехбайтовая команда MOV direct, direct обеспечивает пересылку между двумя любыми ячейками памяти, включая регистры микроконтроллера. Тем не менее, для обмена с регистрами предусмотрены специальные двух- и однобайтовый форматы:

Их использование позволяет существенно сократить длину программного кода. Специальная команда моу ортк, #сЗаСа16 позволяет загрузить 16-разрядный указатель ЭРТЯ значением с!а1а16.

При выполнении команды МОУС считывания данных из программной памяти могут быть применены два способа адресации: по базе ЭРТЯ и относительный. В обоих случаях целое без знака смещение (индекс) хранится в ак-

кумуляторе. Приемником результата также служит аккумулятор. Команда дает возможность выполнять быструю перекодировку по таблицам, осуществлять доступ к массивам памяти. Операции PUSH и POP используют только прямой способ адресации, что не мешает им манипулировать содержимым регистров, которые рассматриваются как ячейки памяти.

Две типовые операции обмена ХСН и XCHD дополняют одностороннюю пересылку двусторонней. При выполнении операции ХСН обмену подлежат байты, при XCHD — младшие тетрады байтовых операндов.

Приведенная в табл. пЗ группа команд логических операций, содержит три типовые двухместные операции: ANL — логическое И, ORL — логическое ИЛИ и XRL — логическое исключающее ИЛИ. Источником первого операнда и одновременно приемником результата служит либо аккумулятор А, либо прямо адресуемая ячейка памяти. Второй операнд задается одним из четырех основных методов адресации. В состав группы входит также ряд одноместных операций: CLR — очистки, CPL —

логического дополнения (инверсия), а также RL, KLC, RR и KRC — операции циклического и расширенного сдвигов вправо и влево. Все операции манипулируют содержимым только аккумулятора А. Сюда же включена операция обмена тетрад в аккумуляторе SWAP, которая может интерпретироваться как циклический сдвиг байта на четыре разряда.

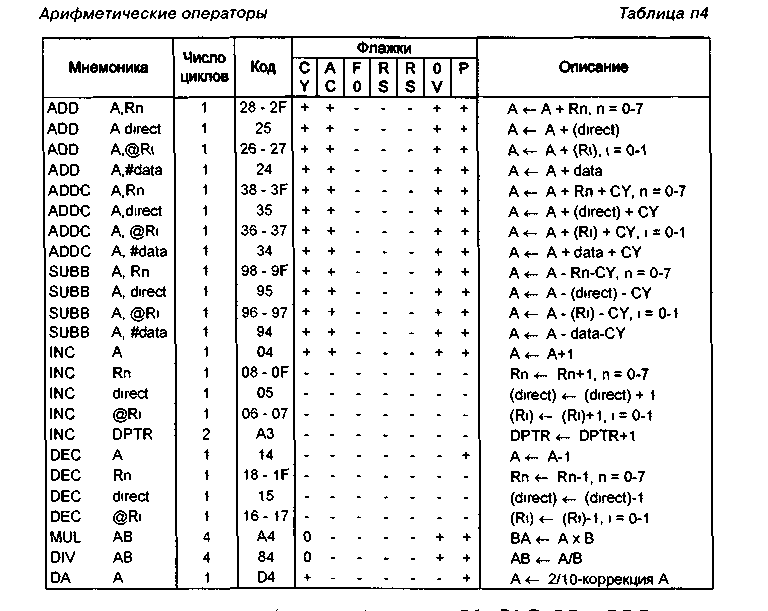

В состав группы команд арифметической обработки (табл. п4) входят: операция сложения ADD, сложения с учетом переноса ADDC, вычитания с учетом займа SUBB, увеличения и уменьшения на единицу 1NC и DEC, десятичная коррекция сложения в 2/10-коде упакованного формата DA, умножение MUL и деление D1U. Операции выполняются над беззнаковыми целыми числами.

В операциях сложения и вычитания первым операндом и приемником результата служит аккумулятор. В качестве второго операнда выступает либо рабочий регистр Rn, n = 0...7, выбранного регистрового банка, либо ячейка памяти данных, адресуемая прямо direct или косвенно @Ri, i = 0-1, либо непосредственные данные #data. Операции 1NC и DEC применимы к ак-

кумулятору, одному из рабочих регистров или к ячейке памяти, адресуемой как прямо, так и косвенно. Кроме этого операция увеличения на единицу может быть применена к содержимому регистра указателя DPTR.

В операциях целочисленного умножения и деления без знака участвуют аккумулятор и регистр В. При умножении 8-разрядное значение А умножается на 8-разрядное значение В, а 16-разрядный результат записывается в пару ВА. При этом регистр В хранит старшую часть произведения. Флажок переполнения OV устанавливается, если произведение больше 255. При делении 8-разрядного значения А на 8-разрядное значение В частное записывается в А, а остаток в В. При попытке деления на 0 устанавливается флажок переполнения. Операция десятичной коррекции для сложения DA осуществляется стандартным способом.

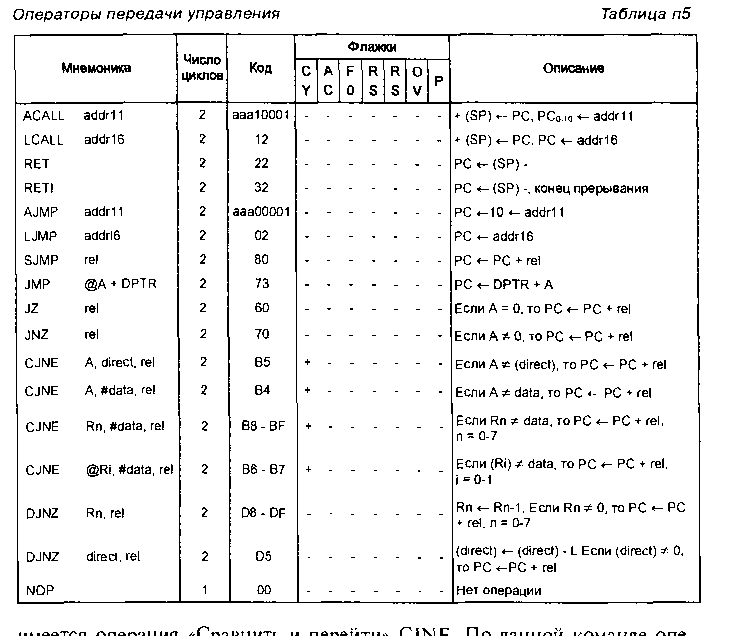

В составе группы команд передачи управления (табл. п5) находятся команды перехода AJMP, LJMP, SJMP, JMP, условного перехода JZ, JNZ, CJNE, вызова ACALL, LCALL, возврата RET, RET1 и модификации с условным переходом DJNZ. Сюда же включена пустая команда NOP.

В командах передачи управления широко применяется относительная адресация, которая поддерживает перемещаемые программные модули. В качестве относительного адреса выступает 8-разрядное смещение ге! со знаком, обеспечивающее ветвление от текущего положения PC в обе стороны на +127 байт. Для перехода в любую другую точку 64К-байто-вого адресного пространства может быть использован либо прямой addrl6, либо косвенный @A+DPTR адрес. В последнем случае содержимое А интерпретируется как целое без знака. Вариант короткой прямой адресации addrll внутри 2К-байтовой текущей страницы введен для совместимости с более старыми процессорами.

Все эти типы адресации могут быть применены только к операции перехода, а для операции вызова допустимы только прямой addrl6 и внутристраничный addrll способы адресации. Во всех условных операциях может использоваться только относительная адресация.

Когда микроконтроллер АТ89С2051 опознает запрос на прерывание, он генерирует одну из команд типа LCALL addrlö, что автоматически обеспечивает запоминание адреса возврата в стеке. При этом логика прерываний перестает срабатывать на запросы того уровня, который был принят к обслуживанию. Для понижения уровня прерывания служит команда возврата из прерывания RET1, которая кроме операции, эквивалентной RET, включает операцию разрешения прерывания данного уровня.

К условным операциям относятся также операторы JZ и JNZ, JC и JNC. Две последние включены в группу булевых. Кроме того, в системе команд

FiiviC/C/ iv* wi ix-рацпл "vpaDnriiD ri jiv^v^ki i ri" v_.j i ч ь, пи даппии \имапд^ ипс-

ранд сначала сравнивается по правилам вычитания целых чисел с константой и в соответствии с результатом сравнения выставляется флажок CY. Затем в случае несовпадения с константой выполняется ветвление. Сравнивая аккумулятор, регистр или ячейку памяти с последовательностью констант, получаем удобный способ проверки на совпадения, например, с целью выявления особых случаев. По сути дела команда CJNE может рассматриваться, как элемент языка высокого уровня типа CASE.

Команда DJNZ — это команда организации программного цикла. В качестве счетчика может использоваться один из рабочих регистров Rn, п=0...7, а так же любая ячейка памяти данных DSEG.

Ряд команд, предназначенных для выполнения операций пересылки, проверки условий и логической обработки булевых (одноразрядных) переменных, образует отдельную группу (табл. пб). В качестве одного из операндов они применяют флажок переноса CY, в качестве другого служит прямо

адресуемый элемент пространства BSEG. Флажок CY при выполнении операций И и ИЛИ может рассматриваться как булевый аккумулятор.

В группу входят также операции безусловного и условного переходов с относительным 8-разрядным смещением rel. Условный переход может быть осуществлен как при установленном JB, так и при сброшенном JNB бите. Особо следует отметить операцию JBC, которая реализует ветвление при установленном бите и одновременно с этим сбрасывает его в 0. Такая операция полезна в системах, решающих много задач, при организации семафоров, которые вводятся для защиты коллективно используемых ресурсов микропроцессора.

Семафор представляет собой расположенный в памяти флажок, информирующий о состоянии связанного с ним ресурса: 1 — свободно; 0 — занято. Захват ресурса допускается только в случае, если он свободен, затем семафор должен быть переведен в состояние «Занято». Захват ресурса с помощью команды JBC осуществляется следующим образом:

WAIT: JBC bit, OK ;Проверка семафора bit

SJMP WAIT .Ресурс занят, ожидание

OK: — ;Ресурс захвачен